Ensuring Semiconductor Durability: Advances in Wafer Level Reliability Testing

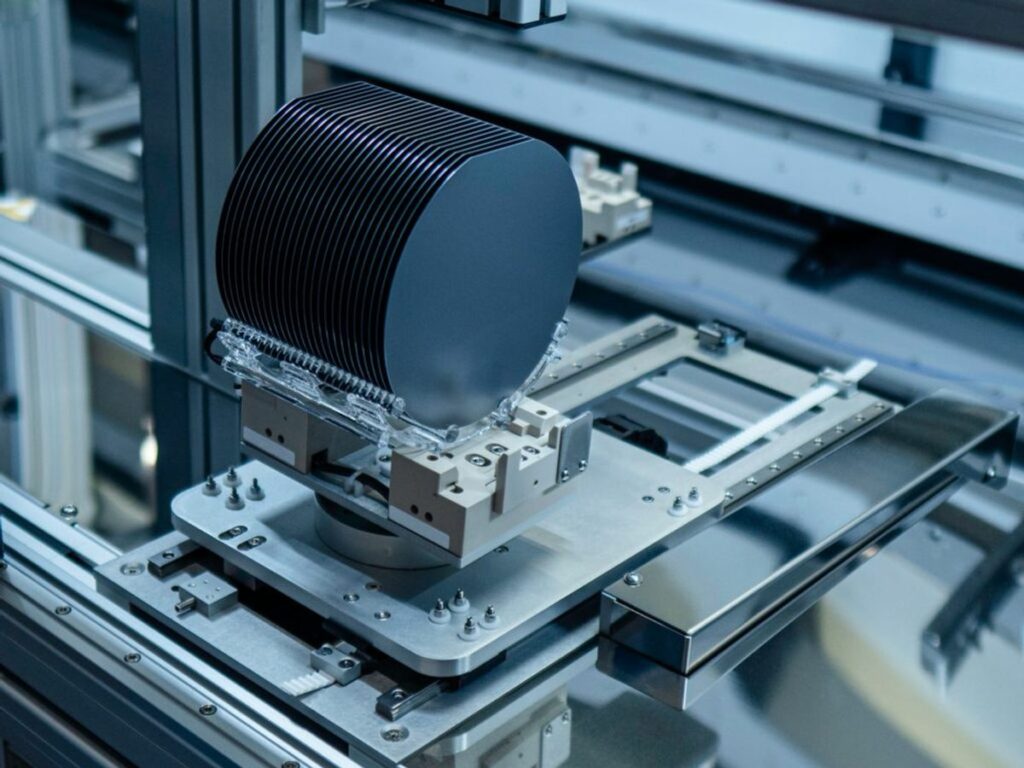

Semiconductor devices are the backbone of modern electronics, and their reliability is crucial for ensuring the performance and longevity of electronic systems. Wafer Level Reliability (WLR) testing plays a vital role in this context by identifying potential wear-out mechanisms and providing insights into the lifespan of semiconductor components. Advances in WLR testing techniques, including predictive modeling, advanced packaging, and design innovations, have significantly enhanced the ability to ensure semiconductor durability. This article delves into the latest developments in WLR testing, exploring how these methods contribute to the robustness of semiconductor devices.

Key Takeaways

- Advanced WLR testing methodologies, such as test-to-fail, help identify and understand wear-out mechanisms, improving predictions for device longevity.

- Predictive modeling using test-to-fail data enables accurate estimations of semiconductor lifespan under various operational environments, benefiting industries from solar energy to autonomous vehicles.

- Challenges in advanced packaging, including thermal issues, electromigration, and crosstalk, are addressed through multi-field coupling reliability studies, optimizing semiconductor performance.

- Design and process innovations, including component reduction and PCB simplification, contribute to enhanced reliability, faster testing, and improved yield of semiconductor devices.

- Future WLR testing will likely incorporate emerging technologies like finite element analysis and Taguchi methods, offering optimized design and reliability for next-generation semiconductors.

Exploring Wear-Out Mechanisms in Semiconductor Devices

Understanding Test-to-Fail Methodology

The test-to-fail methodology is a critical approach in identifying the durability and potential wear-out mechanisms of semiconductor devices. It involves pushing a device to its operational limits to determine the conditions under which it fails. This method provides valuable insights into the intrinsic reliability of the device and helps in formulating robust design and manufacturing processes.

Key steps in the test-to-fail methodology include:

- Defining the stress conditions (e.g., temperature, voltage, current) that simulate the operational environment.

- Applying these conditions to the device until failure occurs.

- Analyzing the failure to identify the underlying wear-out mechanisms.

By systematically stressing devices beyond their normal operating conditions, engineers can uncover latent defects and understand the factors contributing to device failure. This data is essential for improving semiconductor reliability and informs subsequent predictive modeling efforts.

Identifying Common Failure Modes

Semiconductor devices are susceptible to a variety of failure modes that can compromise their performance and longevity. Understanding these failure modes is crucial for improving device reliability and predicting potential issues before they occur. The common failure modes can be broadly categorized into three types: Closed Circuit Failure, Open Circuit Failure, and Degraded Device Failure.

Closed Circuit Failure occurs when unintended paths are created, allowing current to flow where it should not, potentially leading to overheating and damage. Open Circuit Failure is characterized by the interruption of the electrical path, preventing current from flowing through the circuit as designed. Degraded Device Failure refers to the gradual decline in performance due to factors such as material fatigue, electromigration, or thermal stress.

Each failure mode has its root causes and presents unique challenges in wafer level reliability testing. Addressing these issues early in the design and manufacturing process can significantly enhance the durability of semiconductor devices.

Implications for Device Longevity

The longevity of semiconductor devices is a critical aspect of their overall reliability and performance. Understanding the implications of wear-out mechanisms is essential for predicting how long a device will function before failure. This understanding is not only beneficial for improving the design but also for lifecycle management, ensuring that devices outlast the products they power.

The test-to-fail methodology provides valuable insights into the robustness of semiconductor devices. By identifying the conditions that lead to failure, engineers can design devices to withstand real-world stresses. For instance, the impact of die size and bump shape on temperature cycling reliability is a significant factor in the thermo-mechanical wear-out mechanisms.

To address the challenges of device longevity, it is crucial to consider mission-specific reliability predictions. These predictions take into account the unique requirements of applications such as solar energy systems, DC-DC converters, and lidar technologies. The following list outlines key considerations for enhancing device longevity:

- Thermo-mechanical wear-out mechanisms

- Electrical and electromagnetic challenges in high-density interconnects

- Structural complexities and environmental stressors in advanced packaging

- Mission-specific reliability predictions for diverse applications

In conclusion, the integration of test-to-fail data with predictive modeling and design innovations can lead to semiconductors that not only meet but exceed the expected lifespan of the products they are used in.

Predictive Modeling for Semiconductor Lifespan

Leveraging Test-to-Fail Data

The strategic use of test-to-fail data is pivotal in enhancing the predictive accuracy of semiconductor lifespan. By analyzing the results from test-to-fail experiments, engineers can identify patterns and stress responses that are indicative of potential failure mechanisms. This data-driven approach allows for the refinement of predictive models, ensuring that they are closely aligned with real-world conditions.

Adaptive test ramps, a concept emerging in the data intelligence era, underscore the importance of applying the right test content to the device. This involves utilizing data from the tester, on-die sensors, or previous steps to tailor the testing process. Such adaptability leads to more efficient and intelligent testing strategies, ultimately contributing to the reliability of semiconductor devices.

The following table summarizes key aspects of leveraging test-to-fail data in semiconductor reliability testing:

| Aspect | Description |

|---|---|

| Pattern Identification | Analyzing failure data to detect common wear-out mechanisms. |

| Stress Response Analysis | Understanding how devices react under various stress conditions. |

| Predictive Model Refinement | Using empirical data to enhance the accuracy of lifespan predictions. |

| Adaptive Testing | Implementing intelligent test strategies based on comprehensive data analysis. |

Estimating Device Lifetime in Operational Environments

The challenge of accurately estimating the lifetime of semiconductor devices in operational environments is critical for lifecycle management. Ideally, semiconductor products should outlast the products they are integrated into. However, this is not always the case, particularly with standard ICs facing obsolescence threats. A comprehensive understanding of wear-out mechanisms, as highlighted in the current reliability report, is essential for making practical mission scenario predictions.

To address this, statistical models are employed, utilizing accelerated aging data to estimate device lifetimes under various stress conditions. The median lifetime, which represents the time at which the cumulative failure fraction (cff) is equal to 0.5, is a key metric in these analyses. This approach allows for mission-specific reliability predictions, which are crucial for applications ranging from solar energy systems to advanced lidar technologies.

The following table summarizes the estimated lifetimes for different semiconductor devices under standard operational conditions:

| Device Type | Median Lifetime (years) | Mean Lifetime (years) |

|---|---|---|

| Solar Cell | 20 | 21 |

| DC-DC Converter | 10 | 11 |

| Lidar System | 15 | 16 |

These estimates provide a foundation for strategic decisions, such as considering a last time buy (LTB) of wafer supply, which can be stored for extended periods and used to fulfill production orders as needed.

Case Studies: From Solar Cells to Lidar Systems

The predictive modeling of semiconductor lifespan is a critical aspect of reliability testing, and case studies in various applications provide valuable insights. In the realm of solar energy, researchers are actively exploring the influence of thermal effects on the durability of solar cells. A study focusing on perovskite solar cells, for instance, examines the integration of low-cost carbon materials like graphene to mitigate thermal stresses and enhance efficiency.

Lidar systems, used extensively in autonomous vehicles and advanced driver-assistance systems (ADAS), also undergo rigorous lifespan predictions. The pulsed lasers in Lidar are subject to intense operational demands, necessitating comprehensive reliability assessments. By analyzing the performance of Lidar components under simulated environmental conditions, engineers can predict potential failure modes and devise strategies to extend the system’s operational life.

The following table summarizes key findings from recent case studies in both solar cell and Lidar system reliability testing:

| Application | Key Finding | Implication for Reliability |

|---|---|---|

| Solar Cells | Integration of graphene reduces thermal stress | Enhanced efficiency and lifespan |

| Lidar Systems | Pulsed lasers withstand high operational demands | Improved prediction of failure modes |

Advanced Packaging and Multi-Field Coupling Reliability

Thermal, Electromigration, and Crosstalk Challenges

The relentless miniaturization of semiconductor devices has led to increased thermal and electrical densities, which in turn exacerbate thermal migration (TM) and electromigration (EM) issues. These phenomena can induce significant stress on solder bumps and interconnects, accelerating failure rates. Research has shown that the shape of solder bumps, such as cylindrical, hourglass, and barrel-shaped, can influence their susceptibility to EM, with cylindrical bumps often being a more robust choice.

To address these challenges, a multi-pronged approach is necessary. This includes optimizing interconnect structures, adjusting pad opening sizes and bump heights, and refining solder bump layouts. Material selection also plays a critical role, as different materials can mitigate the effects of current crowding and thermal stress. The table below summarizes some of the strategies and their impacts on reliability:

| Strategy | Impact on Reliability |

|---|---|

| Interconnect Optimization | Improves resistance to EM |

| Pad Opening Size Reduction | Reduces current crowding |

| Bump Height Adjustment | Alleviates thermal stress |

| Material Selection | Enhances overall durability |

Furthermore, the reliability of advanced packaging is not only threatened by thermal and electrical challenges but also by crosstalk problems. High-density interconnects are prone to electromagnetic coupling, which can lead to signal interference and degradation of device performance. Understanding the complex interactions between these various physical fields is crucial for developing robust semiconductor devices.

Reliability of Interconnect Structures

Interconnect technology is pivotal in advanced packaging, acting as the main electrical transmission pathway while being highly susceptible to failures. Research on multi-physics coupling reliability has shown that interconnects, such as bumps, redistribution layers (RDLs), and through-silicon vias (TSVs), are prone to issues stemming from the interaction of electrical, thermal, and mechanical stresses.

The reliability of these structures is paramount, as they are often the weakest link in the semiconductor device. Failures can arise from various sources, including thermal cycling, electromigration, and signal crosstalk. For instance, during the manufacturing process, steps like bonding and reflow can introduce thermal stresses that may lead to fatigue failure in flip-chip (FC) bumps. Similarly, operational temperature fluctuations pose a risk of structural failure due to thermal mismatch.

To address these challenges, studies such as those by Banijamali et al. and Fan et al. have focused on the design and optimization of thermo-mechanical reliability in wafer level packaging. These efforts aim to enhance the durability of interconnects and, by extension, the overall device reliability. The table below summarizes key research contributions in this field:

| Reference | Focus Area | Key Findings |

|---|---|---|

| Banijamali et al. | TSV Interposers | Advanced reliability study for 28nm FPGA technology |

| Fan et al. | Thermo-mechanical Reliability | Optimization strategies for wafer level packaging |

Continued research and optimization are essential to mitigate the risks associated with interconnect failures and to ensure the longevity of semiconductor devices.

Optimization Strategies for Thermal Reliability

Optimizing thermal reliability in semiconductor devices is crucial for ensuring their longevity and performance. Advanced packaging technologies have introduced new challenges in managing thermal stresses due to increased density and multi-layer structures. Effective heat dissipation is often hindered, leading to reliability concerns under high-temperature operations and thermal cycling.

To address these challenges, researchers have developed various strategies. One approach involves the design and optimization of thermo-mechanical reliability in wafer level packaging. For instance, studies have shown that using Through-Silicon Vias (TSVs) and bumps for interconnects can lead to thermal mismatch at bonding interfaces, causing structural failures. To mitigate these issues, a combination of material selection, structural design, and simulation techniques are employed.

A notable advancement is the use of 3D IC thermal-mechanical coupling field simulation methods. These methods, such as the equivalent homogenized modeling approach and sub-modeling technique, have significantly improved the accuracy of predicting local temperature and warpage deviations. The table below summarizes key findings from recent studies on thermal reliability optimization:

| Reference | Methodology | Improvement Noted |

|---|---|---|

| Banijamali et al. | TSV interposers and interconnects study | Enhanced reliability for 28nm technology FPGA |

| Fan et al. | Design optimization of thermo-mechanical reliability | Reduced warpage and stress in packaging |

Continued research and development in this area are essential for advancing the durability of semiconductor devices, particularly as the industry moves towards even more densely packed and complex chip architectures.

Enhancing Reliability through Design and Process Innovations

Component Reduction and PCB Simplification

The drive towards component reduction and PCB simplification is a strategic approach to enhance the reliability of semiconductor devices. By integrating many discrete components into a single microchip, significant cost savings and a reduction in the build of materials (BOM) are achieved. This consolidation not only minimizes solution size and weight but also ensures that every silicon area is purposefully utilized for the target application.

The adoption of Wafer-Level Chip Scale Packages (WLCSP) plays a pivotal role in this process. WLCSPs offer the lowest resistance and inductance from die to PCB, coupled with the smallest form factor that mirrors the dimensions of the die. The absence of plastic encapsulation reduces volume and weight, which, in turn, enhances heat dissipation. Moreover, WLCSPs typically eliminate one test insertion in production, streamlining the testing process and improving the final product yield.

The benefits of this approach extend beyond physical attributes:

- Improved reliability due to fewer PCB interconnections

- Expedited and cost-effective PCB testing

- Utilization of chips at the beginning of their lifecycle, guaranteeing optimal performance

- High-density pin configurations that support greater functionality

Ultimately, the shift towards fewer components and simplified PCB designs is not just a matter of efficiency; it’s a strategic choice that directly impacts the longevity and reliability of semiconductor devices.

Advancements in PCB Testing Techniques

The landscape of PCB testing has evolved significantly, with a focus on enhancing the reliability of the final product. Testing PCBs involves using various methods and tools to ensure that all the individual elements of a PCB perform optimally. This comprehensive approach is crucial for assembling a high-quality PCB that is guaranteed to use the chip at the beginning of its lifecycle, thus improving the overall product yield.

Recent advancements have streamlined the testing process, making it faster and more cost-effective. The integration of high-volume production Automated Test Equipment (ATE) and wafer probers has facilitated multi-site testing, which allows for extensive data analysis and wafer mapping. This integration is essential for handling the increased complexity of PCBs as electronic packaging technology progresses from 2D to 2.5D and 3D structures.

The table below summarizes key aspects of the latest PCB testing equipment and capabilities:

| Equipment Type | Features |

|---|---|

| Production ATE | High volume test, final package testing stations, scalable |

| Wafer Probe | 6" & 8" capability, Al pads and solder bumps, fine pitch, high pin count, extended temperature range |

As the industry moves towards more advanced packaging, the role of interconnect technology becomes increasingly critical. It serves not only as an electrical transmission channel but also as a structural component that must withstand various physical stresses. Addressing the challenges in electrical performance and mechanical properties of elements like Through-Silicon Vias (TSVs) and micro-bumps is a key focus area for ongoing research and development in PCB testing.

Improving Yield with Early Lifecycle Chip Utilization

The pursuit of higher yield in semiconductor manufacturing has led to innovative strategies, one of which is the utilization of chips at the earliest stages of their lifecycle. By monitoring chip silicon health and analytics throughout the device lifecycle, manufacturers can ensure that each chip is used when it is most reliable, thereby improving the overall yield of the final product.

Lifecycle management is crucial in this context. It is not uncommon for semiconductor products to fall short of outliving the products they power, particularly when standard ICs are employed. By guaranteeing the use of chips at the beginning of their lifecycle, the risk of obsolescence due to various factors, including commercial underperformance, is mitigated.

The integration of many discrete components into a single microchip not only results in significant cost savings but also leads to a reduction in the build of materials (BOM), and a smaller, lighter solution. A custom design that fully utilizes the silicon for the target application optimizes the total solution, allowing for the addition or removal of specific functions as needed, and balancing performance with power consumption for smarter, more flexible form factors.

Future Directions in Wafer Level Reliability Testing

Emerging Technologies and Their Reliability Implications

As semiconductor technologies advance, new challenges in reliability testing emerge. The integration of novel materials and complex architectures necessitates a reevaluation of traditional testing protocols. For instance, the introduction of 2D materials like graphene and transition metal dichalcogenides (TMDCs) brings forth questions about their long-term stability under electrical stress.

Emerging technologies also include advanced packaging solutions that aim to address the limitations of current interconnect structures. These solutions often involve multi-field coupling, which can lead to new types of wear-out mechanisms. The table below summarizes some of the key emerging technologies and their associated reliability concerns:

| Technology | Concern | Example |

|---|---|---|

| 2D Materials | Electrical Stability | Graphene, TMDCs |

| Advanced Packaging | Multi-field Coupling | 3D ICs, FoWLP |

| Quantum Computing | Qubit Coherence | Superconducting Circuits |

Understanding these implications is crucial for developing robust semiconductor devices that can withstand the rigors of modern applications. It is not only about identifying potential failure modes but also about adapting reliability testing to accommodate the unique properties of these cutting-edge technologies.

The Role of Finite Element Analysis in Reliability Enhancement

Finite Element Analysis (FEA) has become an indispensable tool in enhancing the reliability of semiconductor devices. By simulating various stress factors, FEA allows engineers to predict and mitigate potential failure modes before they occur in real-world applications. This predictive capability is particularly crucial for advanced packaging, where structural failures can arise from thermal issues, electromigration, and signal crosstalk due to electrothermal coupling.

The application of FEA in thermomechanical coupling analysis is a prime example of its utility. Engineers use FEA to model the warpage and cracking of packaging structures, which are often caused by mismatches in the coefficient of thermal expansion (CTE) between different materials. A typical workflow involves establishing a model, applying displacement and temperature boundary conditions, and calculating to obtain the stress distribution within the device.

Recent studies have demonstrated the effectiveness of FEA in improving the mechanical performance and lifespan of Through-Silicon Vias (TSVs). For instance, the use of carbon nanotubes (CNTs) as a filler material has been validated for high reliability in TSVs through orthogonal experimental analysis. Such advancements underscore the role of FEA not just in predictive modeling but also in guiding material selection and design improvements for semiconductor packaging.

Integrating Taguchi Methods for Optimized Design

The integration of Taguchi methods into semiconductor design processes marks a significant advancement in optimizing product quality and reliability. By employing a systematic approach to design optimization, engineers can pinpoint the most influential factors affecting product performance and durability. This approach not only enhances the overall design but also streamlines the development process, leading to more robust semiconductor devices.

Recent research has highlighted the effectiveness of the Taguchi method in various applications within the semiconductor industry. For instance, a study on the thermal reliability of a four-tier die-stacked SiP structure utilized finite element analysis alongside the Taguchi method to achieve optimal results. The method’s ability to handle complex multi-objective optimization problems is particularly beneficial in scenarios where multiple fields, such as thermal, electromagnetic, and structural domains, interact.

The following table summarizes key studies that have successfully integrated Taguchi methods for reliability optimization in semiconductor packaging:

| Study ID | Focus Area | Key Findings |

|---|---|---|

| 57 | Heat Transfer Optimization | Improved heat transfer performance and signal integrity in 3-D chips |

| 53 | Electromagnetic-Circuital-Thermal Co-Simulation | Enhanced transient electromagnetic-circuital-thermal co-simulation accuracy |

| 76 | Multiphysics Coupling Simulation | Effective 2.5D microsystem multiphysics coupling simulation and optimization |

These studies demonstrate the Taguchi method’s versatility and its potential to significantly impact the future of semiconductor manufacturing and design.

Conclusion

The advancements in wafer level reliability testing are pivotal for the semiconductor industry, ensuring that devices can withstand the rigors of real-world applications. This article has explored the various wear-out mechanisms, predictive methodologies, and mission-specific reliability predictions that are critical for the longevity and performance of semiconductor components. The research cited underscores the importance of multi-field coupling reliability studies, particularly in the context of thermal issues, electromigration, and signal transmission crosstalk. As we move towards more complex and miniaturized electronic packages, the role of reliability testing becomes even more crucial. By adopting these advanced testing strategies, manufacturers can improve component reduction, enhance PCB testing efficiency, and guarantee the use of chips at the beginning of their lifecycle, ultimately leading to higher final product yields and more reliable electronic systems.

Frequently Asked Questions

What are the common failure modes in semiconductor devices?

Common failure modes include electromigration, thermal stress, mechanical stress, oxidation, and various forms of corrosion. These failures can be due to manufacturing defects, material impurities, or operational stresses.

How does test-to-fail methodology contribute to semiconductor reliability?

Test-to-fail methodology involves pushing a device to its limits to understand how and why it fails. This data helps engineers design more robust semiconductors by identifying and mitigating potential failure mechanisms.

Can we predict the lifespan of a semiconductor device in its operational environment?

Yes, by using predictive modeling that leverages test-to-fail data, it’s possible to estimate the lifespan of semiconductor devices in their specific operational environments, such as high-temperature conditions or high-frequency applications.

What are the challenges in ensuring the reliability of advanced packaging?

Advanced packaging faces challenges such as thermal management, electromigration, and signal crosstalk. These issues are exacerbated by the multi-field coupling in densely packed semiconductor structures.

How does reducing components on a PCB improve reliability?

Reducing components on a PCB can decrease the potential points of failure, simplify the design, and improve overall reliability. It also facilitates faster and more cost-effective testing and can improve the final product yield.

What is the role of finite element analysis in enhancing semiconductor reliability?

Finite element analysis (FEA) is used to simulate and analyze the physical behavior of semiconductor devices under various conditions. It helps in optimizing designs to improve thermal and mechanical reliability by predicting stress and deformation.