Innovations in Wafer Level Testing: What You Need to Know

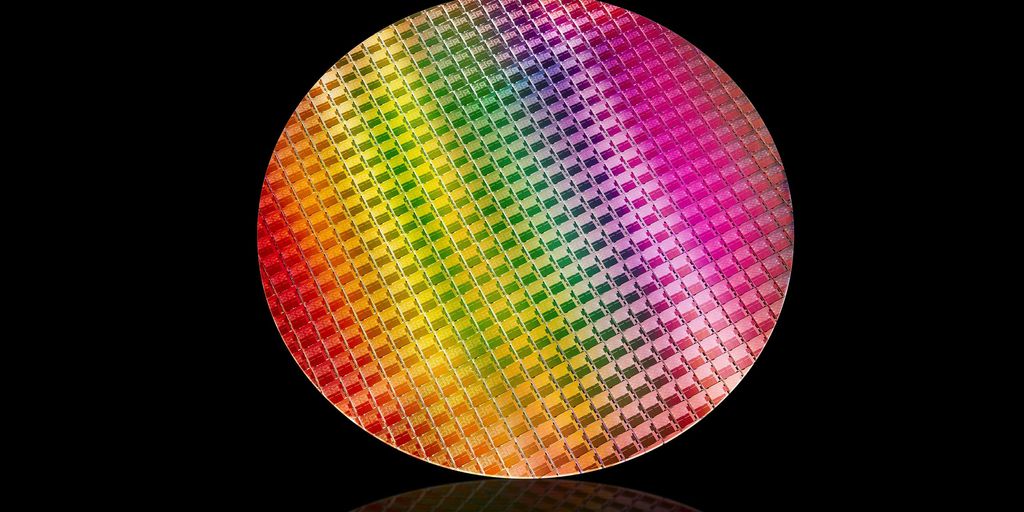

Wafer level testing is a crucial part of making semiconductors. It ensures that each tiny part works correctly before moving on to the next step. This article will look at the methods and new technologies used in wafer testing. It’s important for anyone in the semiconductor industry, from engineers to quality control experts, to understand these processes.

Key Takeaways

- Wafer level testing is essential for ensuring the quality and functionality of semiconductor parts.

- New technologies are making wafer testing more accurate and efficient.

- Challenges like integrating different devices and tracking parts require advanced solutions.

- Future trends include using nanotechnology and 3D integration for better testing.

- Best practices in wafer testing help maintain high standards and improve results.

Understanding Wafer Level Testing

Importance in Semiconductor Manufacturing

Wafer level testing is a crucial step in semiconductor manufacturing. It involves probing individual semiconductor devices on a wafer to identify defects and confirm functionality before further manufacturing. This process ensures that only functional devices proceed to the next stage, saving time and resources.

Key Processes Involved

- Visual Inspection: Technicians examine each wafer for visible flaws like cracks or scratches. This step is vital as physical defects can affect performance.

- Electrical Screening: This involves testing the electrical properties of each device to ensure they meet specifications.

- Data Analysis: The test results are analyzed to understand the causes of defects or performance issues, turning data into actionable insights.

Technological Advances

Recent advancements in wafer level testing technologies have made it possible to handle the intricate requirements of modern semiconductor devices. These innovations include:

- Automated Testing Equipment (ATE): Enhances the speed and accuracy of tests.

- Advanced Probing Techniques: Allows for more precise measurements.

- Data Analytics Tools: Helps in better understanding and improving wafer quality.

Challenges in Wafer Level Testing

Complexities of Heterogeneous Integration

The rise of heterogeneous solutions, where multiple devices are combined into a single package, brings new challenges. Tracking and managing these components during testing becomes more complex. This requires strong part identification and traceability systems to maintain the integrity of each component.

Part Identification and Traceability

Ensuring each part is correctly identified and traceable throughout the testing process is crucial. This helps in maintaining the quality and reliability of the semiconductor devices. Without proper systems in place, it becomes difficult to manage the testing of multiple integrated components.

Electrical Signature Measurements

As semiconductor devices become more advanced, the need for precise electrical signature measurements increases. These measurements provide deeper insights into the performance and potential issues of the devices. However, capturing these minute details requires enhanced validation techniques and next-generation methodologies.

Advanced Packaging and Its Impact on Wafer Level Testing

Integration of Multiple Dies

Advanced packaging techniques now allow for the integration of multiple dies into a single system. This innovation has led to more complex and powerful semiconductor devices. However, it also means that testing each die thoroughly is crucial to avoid defective units. Ensuring each die functions correctly before final packaging is essential.

Cost-Effective Performance

As the demand for high-performance applications grows, so does the need for cost-effective testing methods. Advanced packaging has pushed the boundaries of what is possible, but it has also increased the cost and complexity of testing. Manufacturers must find a balance between performance and cost to stay competitive.

Front-End Characterization Challenges

Front-end characterization involves testing the electrical and physical properties of semiconductor devices before they are fully packaged. This step is critical for identifying potential issues early in the manufacturing process. Advanced packaging techniques have introduced new challenges in this area, requiring more sophisticated testing equipment and methodologies.

Future Trends in Wafer Level Testing

The future of wafer level testing in the semiconductor industry is set for exciting changes. Nanotechnology is leading the way, allowing for more precise and smaller chip designs. This means better performance and more efficient use of space.

Nanotechnology in Testing

Nanotechnology is revolutionizing wafer testing by enabling more accurate and smaller chip designs. This advancement is crucial for improving chip functionality while reducing size.

3D Integration Testing

3D integration testing is becoming more important as chips become more complex. This type of testing helps ensure that all parts of a chip work well together, even when they are stacked in multiple layers.

Innovative Developments

The field is ripe for innovative developments. As demand rises, there’s a significant opportunity for innovation in overcoming challenges like heterogeneous integration and increased interconnect density. By integrating non-volatile memory, collaborating on probing solutions, and advancing automation, the future of wafer testing looks promising.

Best Practices for Wafer Level Testing

Ensuring Quality Control

In the semiconductor industry, high-quality wafer testing is crucial for the reliability and performance of devices. Each type of test wafer, whether it’s a monitor, dummy, defect, or short loop, plays a unique role in maintaining high standards. These wafers, along with the use of wafer probers and comprehensive chip and die tests, significantly contribute to producing reliable and high-quality semiconductor products.

Effective Testing Methodologies

To ensure each wafer is up to the task, it’s essential to follow best practices in wafer testing. This includes using advanced imaging tools to measure critical features and inspect for defects after manufacturing. Engineering teams have long relied on these tools to ensure the highest standards of quality and functionality.

Maintaining High Standards

Wafer test analysis involves evaluating and interpreting data to ensure each semiconductor meets the highest standards. This process is vital for the production of reliable semiconductor devices, which are integral to almost every modern technology. By adhering to these best practices, the semiconductor industry can continue to deliver high-performance and dependable products.

Technological Innovations in Wafer Level Testing

Next-Generation Methodologies

In the era of miniaturization, wafer level testing technologies have become crucial. These advanced methods are designed to handle intricate requirements, ensuring the highest levels of quality control. As semiconductor integration continues to scale, next-generation methodologies are essential to support the complex needs of modern devices.

Enhanced Validation Techniques

Enhanced validation techniques are now required to secure comprehensive coverage through early wafer level testing. By seeking deeper insights from minute electrical signatures measurements, these techniques help improve the overall testing process. This is especially important for multi-die packages and stacked modules, which pose significant front-end characterization challenges.

Probing and Beyond

Probing has always been a key part of wafer level testing, but the future demands even more. Innovations in wafer probe testing solutions are enhancing semiconductor testing precision. These solutions are designed to go beyond traditional probing, addressing the needs of on-wafer passive integration and other advanced technologies.

Conclusion

In conclusion, wafer level testing is a crucial part of making sure that semiconductor devices work well and are reliable. As technology gets smaller and more complex, the need for advanced testing methods becomes even more important. This article has looked at the different methods and new technologies used in wafer testing, showing how important it is to keep high standards of quality control. By understanding and using these testing techniques, the semiconductor industry can keep moving forward, making better and more efficient devices for the future.

Frequently Asked Questions

What is wafer level testing?

Wafer level testing checks each tiny part on a semiconductor wafer to ensure they work before moving to the next step in making chips.

Why is wafer level testing important?

It helps catch problems early, making sure only good parts move forward. This saves time and money in making semiconductors.

What are some challenges in wafer level testing?

Some challenges include handling different types of parts together, keeping track of each part, and measuring tiny electrical signals.

How does advanced packaging affect wafer level testing?

Advanced packaging, like putting multiple parts together, makes testing harder but can also make the final products better and cheaper.

What future trends are there in wafer level testing?

Future trends include using tiny technology (nanotechnology), testing 3D parts, and new ways to test that are even better.

What are best practices for wafer level testing?

Best practices include making sure tests are done right, using good methods, and always keeping high standards.