Optimizing Semiconductor Lifespan: The Role of Wafer Level Burn-In Testing

The semiconductor industry is continuously pushing the boundaries of efficiency and longevity in electronic components. Wafer Level Burn-In (WLBI) testing is a critical process in optimizing the lifespan of semiconductors by exposing them to thermal and electrical stress before they enter the market. This article delves into the role of WLBI testing, the advancements in wide-bandgap semiconductors such as Gallium Nitride (GaN) and Silicon Carbide (SiC), and addresses the challenges and solutions in wafer scale testing. Moreover, it discusses the role of electrical stress in semiconductor reliability, particularly in high-speed Vertical-Cavity Surface-Emitting Lasers (VCSELs).

Key Takeaways

- Wafer Level Burn-In testing is essential for ensuring semiconductor reliability and extending device lifespan by simulating real-world operating conditions.

- Advancements in wide-bandgap semiconductors, such as GaN and SiC, are pivotal for the development of more efficient and reliable power devices.

- Scaling wafer size from 6 inch to 8 inch presents challenges such as managing flatness and thickness variations, which are being addressed through continuous feedback loops and application-optimized technologies.

- Electrical stress, particularly in the form of bias current density, can significantly influence the degradation of semiconductor devices like high-speed VCSELs.

- Ongoing research into the synergistic effects of proton irradiation and electrical stress provides insights into mechanisms of degradation, aiding in the design of more robust semiconductor devices.

Understanding Wafer Level Burn-In Testing

Fundamentals of Burn-In Testing

Burn-in testing, also known as high-temperature operating life (HTOL) testing, is a critical process in semiconductor manufacturing aimed at ensuring long-term reliability of devices. It serves to identify early failures by subjecting components to stresses beyond their normal operating conditions. This preemptive measure is crucial for filtering out potential early-life failures before the devices reach consumers.

The process involves several key steps:

- Elevated temperature exposure to accelerate the aging process and reveal defects.

- Application of electrical stress to mimic operating conditions.

- Continuous monitoring of electrical parameters to detect any signs of failure.

- Analysis of failure data to improve manufacturing processes and materials.

By implementing burn-in testing at the wafer level, manufacturers can assess the robustness of semiconductor devices on a large scale, leading to enhanced product quality and a reduction in post-deployment failures.

Wafer Level vs. Device Level Burn-In

Wafer-level burn-in (WBI) testing is a critical procedure in the semiconductor industry, ensuring the reliability and quality of semiconductor devices. Unlike device-level burn-in, which tests individual chips after they have been diced from the wafer, WBI tests the entire wafer before dicing. This approach offers several advantages:

- Economies of scale: Testing at the wafer level can be more cost-effective, as it allows for simultaneous testing of all devices on a wafer.

- Early detection of failures: WBI can identify defects and failures before the wafer is cut, reducing waste and improving yield.

- Integration with fabrication: WBI can be seamlessly integrated into the semiconductor fabrication process, leading to shorter feedback loops and faster performance improvements.

However, transitioning from 6 inch to 8 inch wafers introduces challenges such as managing flatness and local thickness variations. These issues require sophisticated technologies and continuous improvement cycles to ensure the performance of devices meets the industry standards. As companies like onsemi develop silicon carbide technologies optimized by application, the focus on material quality and defect reduction becomes paramount. The goal is to achieve lower defect densities and improve the mechanical properties of wafers, which are increasingly resembling the characteristics of silicon.

Evaluating the Impact on Semiconductor Lifespan

The longevity of semiconductors is a critical factor in the overall reliability and cost-effectiveness of electronic devices. Wafer Level Burn-In (WLBI) testing plays a pivotal role in ensuring the lifespan of these components by identifying early-life failures and stress-induced defects that could lead to premature failure in the field.

WLBI testing subjects semiconductor wafers to elevated temperatures and electrical stress before they are diced into individual chips. This process can reveal potential reliability issues that might only surface after prolonged use. By addressing these issues early, manufacturers can enhance the quality and durability of their products.

The impact of WLBI on semiconductor lifespan can be quantified by comparing the failure rates before and after implementing WLBI. Here is a simplified representation of such data:

| Stage | Failure Rate (Before WLBI) | Failure Rate (After WLBI) |

|---|---|---|

| Initial Testing | 2% | 0.5% |

| After 6 Months | 5% | 1% |

| After 1 Year | 10% | 2% |

These figures illustrate the effectiveness of WLBI in reducing the incidence of early failures, thereby extending the operational life of semiconductors. It is important to note that the specific values will vary based on the type of semiconductor, the testing conditions, and the quality of the manufacturing process.

Advancements in Wide-Bandgap Semiconductors

GaN and SiC Material Properties

Wide-bandgap (WBG) semiconductors such as Gallium Nitride (GaN) and Silicon Carbide (SiC) are revolutionizing the field of power electronics. GaN is particularly noted for its high electron mobility, which enables high-frequency, high-power applications and rapid power switching. SiC, on the other hand, excels in handling higher voltages and temperatures, making it ideal for electric vehicle applications where reducing losses and model size is crucial.

The material properties of SiC and GaN are compared below, highlighting their advantages over traditional silicon:

| Property | Silicon (Si) | Silicon Carbide (SiC) | Gallium Nitride (GaN) |

|---|---|---|---|

| Bandgap (eV) | 1.1 | 3.2 | 3.4 |

| Electron Mobility (cm^2/Vs) | Low | Moderate | High |

| Thermal Conductivity (W/mK) | Moderate | High | Moderate |

Cost-effectiveness is another critical factor in the adoption of WBG semiconductors. While SiC manufacturing remains expensive due to high energy usage, GaN is projected to become as cost-effective as silicon in the near future. This economic advantage, coupled with its performance benefits, positions GaN for a bright future in markets currently dominated by SiC, such as several-hundred kilowatt applications.

Improvements in Substrate Quality and Manufacturing

The quest for optimizing semiconductor performance has led to significant advancements in substrate quality and manufacturing techniques. Silicon carbide (SiC) substrates, pivotal in SiC-based power devices, have seen improvements that enhance device performance and reliability. The transition to larger wafer diameters, compatible with traditional silicon wafers, marks a notable development in substrate manufacturing. This shift from approximately 50 mm to 200 mm diameters facilitates the integration of SiC substrates into existing manufacturing infrastructures.

Despite these advancements, challenges remain in achieving the desired material quality. A high density of critical defects persists, necessitating further research and development to reduce these imperfections. Additionally, the mechanical properties of modern wafers have improved, yet issues such as flatness and local thickness variations still require attention. Addressing these concerns is crucial for the continued evolution of substrate properties, particularly for future SiC power devices.

In the context of GaN-based power devices, the choice of substrate material significantly impacts device performance and manufacturability. The well-understood nature of silicon carbide as a substrate material offers a considerable advantage, allowing for the rapid development of cutting-edge devices for various applications. Researchers are actively working to overcome substrate-related challenges, ensuring that GaN devices can meet the high standards of reliability and performance demanded by the industry.

Comparative Analysis: GaN vs. SiC in Power Devices

The debate between Gallium Nitride (GaN) and Silicon Carbide (SiC) in the realm of power devices is pivotal for the future of power electronics. GaN is anticipated to reach or even undercut silicon’s cost within the next one to two years, positioning it as a strong contender against SiC, especially as power levels escalate to several-hundred kilowatts, a domain traditionally dominated by SiC.

GaN’s superior electron mobility and its ability to switch power rapidly make it suitable for high-frequency, high-power applications. On the other hand, SiC’s robustness allows it to handle higher voltages and temperatures, which is crucial for applications such as electric vehicles where reducing losses and model size is beneficial.

Despite GaN’s cost-effectiveness and performance advantages, there are engineering challenges that need to be addressed. SiC, while more expensive in terms of material and energy consumption during manufacturing, remains competitive due to its ability to operate under extreme conditions. The following table summarizes the key differences:

| Property | GaN | SiC |

|---|---|---|

| Bandgap Energy (eV) | 3.4 | 3.2 |

| Electron Mobility | High | Moderate |

| Power Switching | Fast | Slower |

| Voltage Tolerance | Moderate | High |

| Thermal Tolerance | Moderate | High |

As the industry continues to innovate, the choice between GaN and SiC will largely depend on the specific requirements of the power device application, with both materials offering distinct advantages.

Challenges and Solutions in Wafer Scale Testing

Scaling from 6 inch to 8 inch Wafers

The transition from 6 inch to 8 inch wafers is a critical step in semiconductor manufacturing, offering the potential for increased yield and efficiency. However, this shift introduces new challenges, such as managing the flatness and local thickness variations that are more pronounced in larger wafers. These variations can affect the uniformity of the devices produced and must be addressed to ensure high-quality output.

To tackle these issues, manufacturers like onsemi have developed algorithm-based methods to screen devices throughout the fabrication process. This approach, coupled with vertical integration, allows for shorter feedback loops that are essential for rapid performance improvements. The industry’s current standard is predominantly 6 inch wafers, where many of the initial problems have been resolved. As we move towards 8 inch wafers, the lessons learned from the 6 inch processes are invaluable.

The table below outlines the progress in SiC crystal growth, highlighting the benefits of scaling up to 8 inch wafers:

| Diameter | Defect Density | Compatibility | Margin Benefits |

|---|---|---|---|

| 6 inch | Resolved | Established | Moderate |

| 8 inch | Comparable | In Progress | Higher |

The transition not only promises improvements in substrate quality but also aligns with the escalating demand for silicon carbide technologies. Once the technological challenges are overcome, manufacturers can expect gross margin benefits from reduced edge losses and a higher yield of usable chips per wafer.

Addressing Flatness and Thickness Variations

In the pursuit of semiconductor perfection, addressing the challenges of wafer flatness and thickness variations is crucial. These variations can lead to significant performance issues in the final semiconductor devices. To mitigate these issues, industry experts are turning to advanced surface-finishing solutions.

Applied to both sides of the wafer, polishing techniques are now able to achieve some of the lowest Total Thickness Variation (TTV) values in the industry. This not only enhances the efficiency of SiC wafers but also contributes to cost reductions. The table below summarizes the impact of surface-finishing on TTV values:

| Surface-Finishing Technique | Average TTV Reduction |

|---|---|

| Chemical Mechanical Planarization (CMP) | 20% |

| Precision Lapping | 15% |

| Customized Polishing | 25% |

It’s evident that the mechanical properties of modern wafers are increasingly resembling those of silicon, which means that the industry’s next steps must include a focus on reducing defect densities and improving material quality. These improvements are essential for leveraging sophisticated technologies and achieving the desired mechanical characteristics.

Short Feedback Loops for Performance Improvement

In the realm of wafer scale testing, the implementation of short feedback loops is crucial for rapid performance enhancement. These loops allow for immediate adjustments in the testing process, leading to a more efficient identification and resolution of defects. By analyzing data in real-time, engineers can make informed decisions that directly impact the quality and reliability of the semiconductor devices.

The benefits of short feedback loops are manifold. They facilitate a dynamic testing environment where continuous improvement is possible. Below is a list of advantages that these feedback mechanisms provide:

- Accelerated detection of process anomalies

- Enhanced yield through iterative refinement

- Reduction in time-to-market for semiconductor products

Ultimately, the goal is to establish a system where the effects of a perturbation are quickly identified and addressed, thereby minimizing its impact on the production line. This approach echoes the concept of positive feedback in systems theory, where the response to a change is to amplify it, in this case, to expedite the improvement process.

The Role of Electrical Stress in Semiconductor Reliability

Synergistic Effects of Proton Irradiation and Electrical Stress

The interplay between proton irradiation and electrical stress is critical in determining the reliability of high-speed vertical-cavity surface-emitting lasers (VCSELs). The synergistic effect of 3MeV proton irradiation and electrical stress on 850 nm high-speed VCSELs is investigated, revealing that the presence of bias current can significantly influence the rate of device degradation. Under lower bias currents, the degradation of VCSELs appears to slow down, suggesting a protective effect against the harsh conditions induced by irradiation.

However, when devices are subjected to higher bias current densities, the degradation becomes more severe. This indicates that the bias current density plays a pivotal role in the resilience of VCSELs to proton irradiation. The table below summarizes the observed effects of varying bias current densities on VCSEL degradation during proton irradiation:

| Bias Current Density | Degradation Rate |

|---|---|

| Low | Slowed Down |

| High | Accelerated |

The findings from this study not only shed light on the mechanisms of degradation but also underscore the importance of considering electrical stress in the context of radiation hardness for optical communication systems. The implications are particularly significant for VCSELs operating in radiation-prone environments, where ensuring device reliability is paramount.

Bias Current Density and Device Degradation

The reliability of semiconductors, particularly high-speed Vertical-Cavity Surface-Emitting Lasers (VCSELs), is critically affected by the bias current density during operation. At certain levels, bias current density can mitigate the degradation of device performance, especially when subjected to environmental stresses such as proton irradiation. This phenomenon has been observed in 850 nm high-speed GaAs-based VCSELs, where a bias current density of 6.03 imes 10^5 A/m^2 showed a reduced degradation in modulation bandwidth compared to an unbiased state.

The interplay between electrical stress and irradiation is complex, with the bias current density playing a dual role. While it can slow down the degradation process, high bias current density during irradiation can exacerbate device degradation. This is evidenced by the formation of defects, such as electron traps, which are influenced by the bias current. The table below summarizes the impact of different bias current densities on VCSEL degradation:

| Bias Current Density (A/m^2) | Degradation Impact |

|---|---|

| Unbiased | Moderate |

| 6.03 imes 10^5 | Reduced |

| High (unspecified) | Severe |

Understanding the mechanisms behind these effects is crucial for improving the reliability and performance of semiconductors in demanding applications like spatial data communication. The findings from studies on the synergistic effects of proton irradiation and electrical stress provide valuable insights into optimizing semiconductor lifespan through careful management of bias current density.

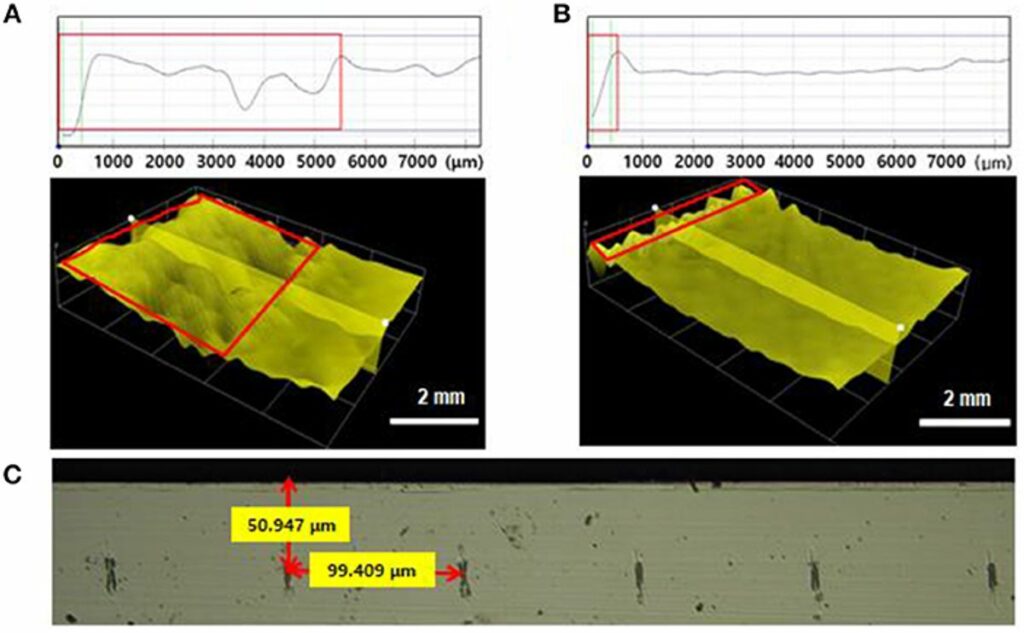

Mechanisms of Degradation in High-Speed VCSELs

The reliability of high-speed Vertical-Cavity Surface-Emitting Lasers (VCSELs) is crucial for applications in data communication and sensing. Degradation of VCSELs is influenced by factors such as proton irradiation and electrical stress, which can lead to a decline in optical-electrical performance over time. Studies have shown that the degradation process can be slowed by the application of bias current, but becomes more severe under high bias current density.

Key factors contributing to VCSEL degradation include:

- Defects induced by proton irradiation

- High bias current density during irradiation

- Electro-Static Discharge (ESD)-induced defect evolution

Recent research has focused on the characterization of photoelectric degradation and the observation of ESD-induced defect evolution. This approach has been instrumental in pinpointing the location and patterns of ESD damage, thereby enhancing our understanding of the degradation mechanisms affecting VCSELs.

Conclusion

In summary, wafer level burn-in testing emerges as a pivotal process in enhancing the reliability and lifespan of semiconductors, particularly as the industry transitions to larger wafer sizes and embraces wide bandgap materials like GaN and SiC. The meticulous examination of wafers for flatness, thickness variations, and other defects is crucial for the deployment of sophisticated technologies. As we have seen, onsemi’s approach to continuous feedback loops and application-optimized silicon carbide technologies exemplifies the industry’s commitment to advancing substrate quality and manufacturing techniques. Moreover, studies on the synergistic effects of proton irradiation and electrical stress on devices like VCSELs underscore the importance of understanding degradation mechanisms to improve device performance. The insights gained from such research are invaluable for informing future innovations and ensuring the robustness of power electronics in an era of rapid technological evolution.

Frequently Asked Questions

What is wafer level burn-in testing and how does it differ from device level testing?

Wafer level burn-in testing involves stressing semiconductor wafers at elevated temperatures and voltages to identify and eliminate early failures before they are packaged. It differs from device level testing, which is performed on individual chips after they have been cut from the wafer and packaged.

How does wafer level burn-in testing impact the lifespan of semiconductors?

By identifying and eliminating early-life failures, wafer level burn-in testing can significantly improve the overall reliability and lifespan of semiconductor devices by ensuring only robust devices make it to market.

What are wide-bandgap semiconductors and why are they important?

Wide-bandgap semiconductors, such as Gallium Nitride (GaN) and Silicon Carbide (SiC), have larger band gaps than traditional silicon, allowing them to operate at higher temperatures, voltages, and frequencies. This makes them crucial for high-power and high-frequency applications.

What challenges arise when scaling wafer level testing from 6 inch to 8 inch wafers?

Scaling to larger wafers introduces challenges such as maintaining uniformity in flatness and thickness, which are critical for the performance of advanced semiconductor devices. This requires sophisticated technologies and continuous improvement in testing processes.

How does electrical stress affect the reliability of high-speed VCSELs?

Electrical stress, particularly when combined with other stressors like proton irradiation, can lead to degradation of optical-electrical parameters in VCSELs. Understanding the mechanisms of this degradation is key to improving their reliability and performance.

What advancements have been made in substrate quality and manufacturing for SiC power devices?

Recent advancements in substrate quality and manufacturing techniques for Silicon Carbide (SiC) have led to improved device performance, reduced defects, and enhanced reliability. However, ongoing development is needed to further optimize substrate properties for future SiC power devices.