The Future of Technology: Exploring the Wafer Scale Package

Technology is always changing, and one of the latest innovations is the Wafer Scale Package. This technology could change how we think about computer chips. It aims to make them faster, smaller, and more cost-effective. Let’s dive into what Wafer Scale Packages are and why they matter.

Key Takeaways

- Wafer Scale Packages offer improved performance compared to traditional packaging methods.

- They provide better scalability and integration for advanced computing needs.

- Cost efficiency is a significant advantage of Wafer Scale Packages.

- Challenges include design complexities, yield issues, and thermal management.

- Future trends point to more applications in AI, data centers, and high-performance computing.

Understanding Wafer Scale Package Technology

Defining Wafer Scale Package

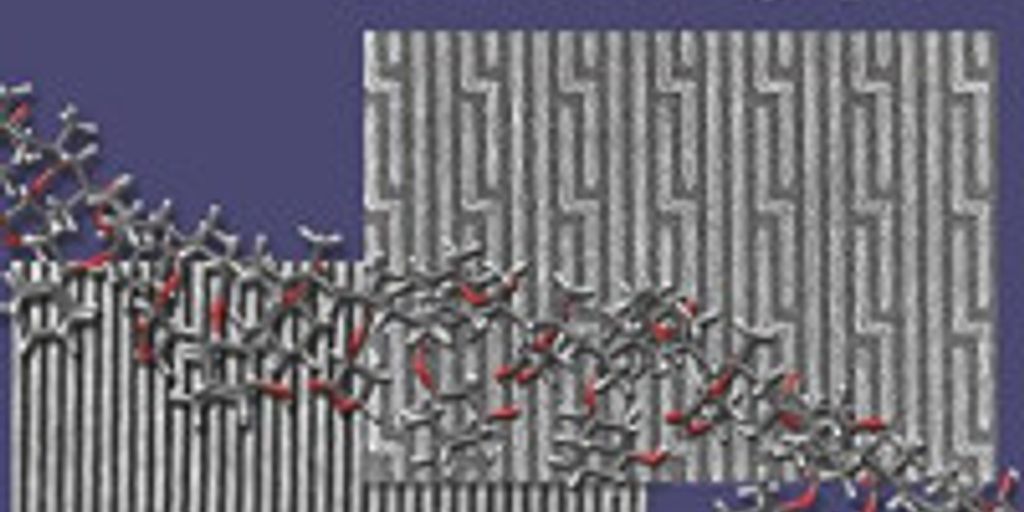

Wafer Scale Package (WSP) technology is a method where the entire silicon wafer is used as a single package. This allows for the creation of highly specialized and functional devices. Unlike traditional methods that cut the wafer into individual chips, WSP keeps the wafer intact, making electrical connections and molding at the wafer level before slicing the chips.

Historical Context and Evolution

The journey of WSP technology began as an experimental approach in the realm of advanced packaging. Over time, it has evolved significantly, driven by the relentless pursuit of miniaturization in integrated circuits (ICs). Traditional packaging methods have reached their physical limits, paving the way for advanced wafer-level packaging (AWLP) techniques that offer tighter integration and enhanced performance.

Key Components of Wafer Scale Packages

WSP technology involves several key components:

- Integration of Passive Components: Embedding passive components like capacitors and resistors directly within the package.

- Advanced Manufacturing Processes: Innovations in photolithography, etching, and deposition techniques are crucial for achieving the required precision and density.

- System Design Co-Optimization: There is a need for systematic design principles to determine the appropriate wafer-scale substrate techniques and layout, yield issues, and to co-optimize the packaging and system design.

Advantages of Wafer Scale Packages

Performance Enhancements

Wafer scale packages offer significant performance improvements. The main advantage is in the interconnects—by wiring processors together on-chip, the wafer-scale chip bypasses many of the computational speed losses that come with traditional methods. This results in faster data processing and reduced latency.

Scalability and Integration

One of the standout features of wafer scale packages is their scalability. These packages can integrate a large number of components on a single wafer, making it easier to scale up systems without the need for multiple chips. This is particularly beneficial for applications requiring high levels of integration and compact designs.

Cost Efficiency

Wafer scale packages can also be more cost-effective. By performing essential packaging steps directly on the wafer before dicing it into individual chips, manufacturers can reduce the overall cost of production. This method minimizes material waste and simplifies the manufacturing process, leading to lower costs for end-users.

Challenges in Implementing Wafer Scale Packages

Design and Layout Complexities

Wafer scale packages come with significant design and layout challenges. The hardware footprint is much larger than traditional chips, which means conventional design methods don’t work well. Engineers need to develop new design principles to handle these larger spaces effectively.

Yield and Reliability Issues

One of the biggest hurdles is yield. When working on such a large scale, even a small defect can ruin the entire wafer. This makes it hard to achieve high reliability. Manufacturers must find ways to improve yield rates to make wafer scale packages more viable.

Thermal Management

Managing heat is another major issue. Larger chips generate more heat, and it’s tough to keep them cool. Effective thermal management solutions are essential to ensure the longevity and performance of wafer scale packages.

Advanced Packaging Techniques for Wafer Scale Packages

2.5D and 3D Packaging

2.5D and 3D packaging are innovative methods that stack multiple layers of integrated circuits (ICs) to enhance performance and reduce space. These techniques allow for better communication between layers, leading to faster data transfer and improved efficiency. 2.5D packaging uses an interposer to connect the chips, while 3D packaging stacks the chips directly on top of each other.

Fan-Out Wafer-Level Packaging

Fan-Out Wafer-Level Packaging (FOWLP) is a method where the ICs are placed on a wafer and then encapsulated in a mold compound. This technique allows for a higher density of connections and better thermal performance. FOWLP is particularly useful for applications that require compact and efficient designs.

Interposer Materials

Interposers are materials used in 2.5D packaging to connect different ICs. They play a crucial role in ensuring efficient communication between the layers. Common interposer materials include silicon and organic substrates. The choice of material can impact the overall performance and cost of the wafer-scale package.

Future Trends in Wafer Scale Package Technology

Emerging Applications

Wafer scale packages are opening doors to new and exciting applications. Advanced packaging is reshaping the chip industry by enabling more complex applications like artificial intelligence and machine learning. These technologies require high performance and efficient integration, which wafer scale packages can provide.

Innovations in Fabrication Processes

The fabrication processes for wafer scale packages are constantly evolving. New techniques are being developed to improve yield and reliability. For instance, multichip packaging is becoming more common, allowing for better support of complex applications. However, this also means that new business models are needed for players in the chip industry.

Market Forecasts and Opportunities

The market for wafer scale packages is expected to grow significantly in the coming years. This growth is driven by the increasing demand for high-performance computing and data centers. As more companies adopt these technologies, the opportunities for innovation and development in wafer scale packages will continue to expand.

Comparing Wafer Scale Packages with Traditional Packaging Methods

Size and Density

Wafer scale packages (WSP) offer a significant advantage in terms of size and density. Traditional packaging methods involve dicing the silicon wafer into individual chips and then attaching these chips to a printed circuit board (PCB). In contrast, wafer-level packaging makes the electrical connections and molding at the wafer level before dicing the chips using a laser. This approach allows for a much higher density of components, leading to smaller and more compact devices.

Performance Metrics

When it comes to performance, wafer scale packages often outperform traditional methods. The integration at the wafer level reduces the distance that electrical signals need to travel, which can result in faster processing speeds and lower power consumption. This is particularly beneficial for high-performance computing applications where speed and efficiency are crucial.

Use Cases and Applications

Wafer scale packages are increasingly being used in advanced applications such as high-performance computing, artificial intelligence, and data centers. Traditional packaging methods, while still prevalent, are reaching their physical limitations and are less suited for these cutting-edge applications. As a result, advanced packaging came along to improve system performance compared to traditional packages and deal with size constraints.

Case Studies and Real-World Applications

High-Performance Computing

In the world of high-performance computing, wafer scale packages are making a significant impact. These packages offer high-density, low-latency, and high-bandwidth connectivity, which is crucial for complex computations. For instance, Cerebras Systems has developed a scalable interconnection architecture based on wafer scale technology, enabling faster data processing and improved performance.

Artificial Intelligence and Machine Learning

Wafer scale packages are also revolutionizing artificial intelligence and machine learning. Companies like Cerebras Systems are at the forefront, using this technology to accelerate natural language processing and other AI tasks. This has led to advancements in various fields, including healthcare, where AI models are being used for diagnostic purposes.

Data Centers and Cloud Computing

Data centers and cloud computing services benefit greatly from wafer scale packages. These packages provide the necessary infrastructure for handling large volumes of data efficiently. The new wafer-scale packaging and high-speed wireline technologies offer high-density, low-latency, and high-bandwidth connectivity, making them ideal for modern data centers.

Conclusion

The future of technology, especially in the realm of wafer-scale packaging, is both exciting and challenging. While current advanced packaging technologies are still in experimental stages, they hold immense potential for revolutionizing the way we design and build electronic devices. As these technologies mature, they promise to enable larger, more powerful chips without significant changes to existing manufacturing processes. This means we can expect faster, more efficient devices in the near future. However, to fully realize these benefits, systematic design principles and optimized packaging methods are essential. The journey ahead is filled with opportunities for innovation and improvement, making it an exciting time for the tech industry.

Frequently Asked Questions

What is a wafer scale package?

A wafer scale package is a type of advanced technology where an entire wafer is used as a single, large chip. This helps in improving performance and integration.

How does wafer scale packaging improve performance?

Wafer scale packaging boosts performance by reducing the distance data has to travel, which speeds up communication between different parts of the chip.

What are the main challenges of wafer scale packages?

The main challenges include complex design and layout, issues with yield and reliability, and managing heat effectively.

What are some advanced packaging techniques used in wafer scale packages?

Advanced techniques include 2.5D and 3D packaging, Fan-Out Wafer-Level Packaging, and using different interposer materials.

Where are wafer scale packages used?

They are often used in high-performance computing, AI and machine learning, and data centers and cloud computing.

What is the future of wafer scale package technology?

The future looks promising with emerging applications, innovations in fabrication processes, and growing market opportunities.